Flip-Flops

- RS latches

- level clocking

- D latches

- Edge-Triggered D flip flops

- Edge-Triggered JK flip flops

- JK master-slave flip flops

latches and flip-flops

- memory elements

- two stable states

- remain in one state until triggered into the other

RS latches

- set-reset

- transistor RS latch

- race condition if both inputs are high (low), the final state

is indeterminate (indicated by a "*" in the truth table)

- timing diagram

| R | S | Q | state |

|

0 | 0 | NC | no change |

|

0 | 1 | 1 | set |

|

1 | 0 | 0 | reset |

|

1 | 1 | * | race |

|

|

Switch debouncer

- single-pole, double-throw switch

- open (disconnected) input is high, or can connect to Vcc via a resistor

- metal rubs on metal and contact is made and broken several times

before the contacts come to rest

- we would like a simple, reliable transition

- solution: use RS latch

Clocked latch

- R and S fed through (N)AND gates controlled by a clock

- latch is only controlled when clock is high (low for negative clocking)

- R and S can change arbitrarily while clock is low

- race condition when: clock high, R high, S high

Clocked latch truth table

| CLK | R | S | Q |

|

0 | 0 | 0 | NC |

|

0 | 0 | 1 | NC |

|

0 | 1 | 0 | NC |

|

0 | 1 | 1 | NC |

|

1 | 0 | 0 | NC |

|

1 | 0 | 1 | 1 |

|

1 | 1 | 0 | 0 |

|

1 | 1 | 1 | * |

|

|

D latch

- to avoid race condition, drive R and S from same (inverted) input

- that way, we never have a race condition

- clocked:

- high clock makes the latch transparent, so Q follows D

- low clock makes the latch output fixed

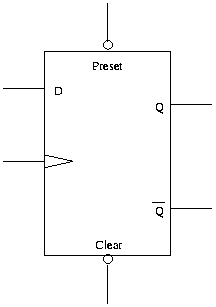

Edge triggering, preset and clear

- often we don't want the value of Q to follow D while CLK is high

- use a capacitor/resistor to generate a carefully controlled

spike when the clock goes from low to high

- that spike is used as the D clocking signal.

- Also, an additional AND gate on the R and S lines can be

used to set or clear the flip flop

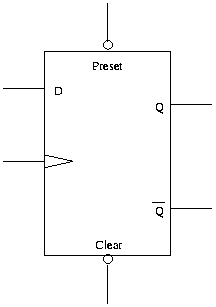

Edge-triggered J-K flip flop

- when J and K are both low, circuit is stable

- high J sets the circuit on the rising clock edge

- high K resets the circuit on the rising clock edge

- high J and K toggles the circuit on the rising clock edge

- if the clock pulse is too wide, circuit toggles more

than once, or races

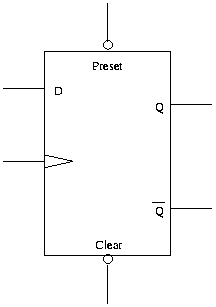

Edge-triggered J-K Master-Slave flip flop

- J-K level triggered flip-flop

- feeds into R-S negative-level triggered flip-flop

- when clock is high, master is active

- when clock is low, master is fixed, slave is active

- if J and K are both high, master toggles when the clock

is high, slave toggles when the clock is low

- cocking -- preparing, on clock high -- and triggering

-- bringing to the outputs, on falling clock

- clock generator